Innovotek -News & BLOG

A blog about the news of the latest technology developments, breaking technology news, Innovotek Latest news and information tutorials on how to.

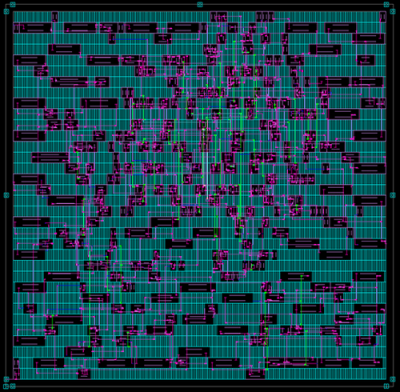

IC compiler enables faster design closure

- Font size: Larger Smaller

- Hits: 11288

- 0 Comments

- Subscribe to this entry

- Bookmark

Synopsys Inc. is offering the IC Compiler 2010.03, a physical implementation solution delivering up to 2.5x faster performance on multicorner/multimode (MCMM) designs, and enhanced in-design technology for faster design closure.

Synopsys Inc. is offering the IC Compiler 2010.03, a physical implementation solution delivering up to 2.5x faster performance on multicorner/multimode (MCMM) designs, and enhanced in-design technology for faster design closure.

IC Compiler's In-Design technology helps prevent late-stage surprises by enabling signoff-accurate static timing analysis, rail analysis and physical verification during design. The new software release has production support for all known 28/32nm design rules for major foundries, with several customer tapeouts underway.

IC Compiler 2010.03 offers performance improvements across the board. It provides 2x faster time to initial floorplan creation and on-demand loading, which offers 2x to 3x faster time to final floorplan creation. IC Compiler 2010.03 also includes 2x faster pre-route feasibility engines and generates interactive reports that help significantly reduce iterative cycles during early stages of design. Faster MCMM scenario processing, core engine improvements and multimode clock tree synthesis deliver faster timing convergence.

Traditional implement-then-verify approaches result in lengthy design iterations due to late-stage surprises. IC Compiler's In-Design technology dramatically reduces such iterations by enabling signoff accurate analysis and physical verification during design. In-Design enhancements in the 2010.03 release include dynamic rail analysis with PrimeRail and DRC auto fixing with IC validator. The 2010.03 release introduces a new leakage optimization engine capable of handling more than 20 leakage variants. This is achieved by using In-Design technology with PrimeTime to deliver considerable leakage reduction while preserving signoff timing. This capability, combined with advances in post-route leakage optimization and MCMM leakage scenario optimization, enables IC Compiler 2010.03 to deliver double the leakage savings in half the time.

IC Compiler 2010.03 is available today and includes a quad-core license enabling multicore processing as a standard feature.