Innovotek -News & BLOG

A blog about the news of the latest technology developments, breaking technology news, Innovotek Latest news and information tutorials on how to.

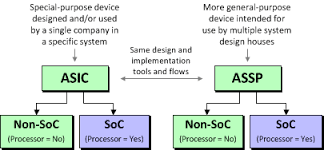

ASIC/SoC designs: Custom corner characterisation

- Font size: Larger Smaller

- Hits: 13678

- 0 Comments

- Subscribe to this entry

- Bookmark

These days, a typical corner (TT) is no longer typical for most applications. For that matter, standard PVT Corners (FF/TT/SS), generally, do not represent the exact environmental conditions in which an ASIC/SoC will be functioning. This means the voltage may not be a nominal Vdd in a typical case or Vdd±10% in an extreme case; and the temperature may not be 25C in a typical case or 125C/-40C in extreme cases. Also, in today's market, everyµW of power saved, and nS of delay avoided, makes a significant difference in a product's performance and cost. Therefore, it is important to know how a system behaves under real-time PVT conditions. One needs to characterise foundation IPs at these special (custom) corners to avoid overdesign and achieve optimal product for best power and performance. When estimating the power and timing numbers of an IP at a custom corner (e.g., @95C and Vdd+3%), it is not easy to derive values from regular SS, TT, and FF characteristics as these may not support linear extrapolations. Even small errors in calculation can be very risky. One approach is to use characterisation tools (e.g., Silicon Smart from Synopsys) that can easily characterise foundation IPs to estimate power and performance of an SoC at any custom corner with substantial accuracy using reference ".lib" files.

These days, a typical corner (TT) is no longer typical for most applications. For that matter, standard PVT Corners (FF/TT/SS), generally, do not represent the exact environmental conditions in which an ASIC/SoC will be functioning. This means the voltage may not be a nominal Vdd in a typical case or Vdd±10% in an extreme case; and the temperature may not be 25C in a typical case or 125C/-40C in extreme cases. Also, in today's market, everyµW of power saved, and nS of delay avoided, makes a significant difference in a product's performance and cost. Therefore, it is important to know how a system behaves under real-time PVT conditions. One needs to characterise foundation IPs at these special (custom) corners to avoid overdesign and achieve optimal product for best power and performance. When estimating the power and timing numbers of an IP at a custom corner (e.g., @95C and Vdd+3%), it is not easy to derive values from regular SS, TT, and FF characteristics as these may not support linear extrapolations. Even small errors in calculation can be very risky. One approach is to use characterisation tools (e.g., Silicon Smart from Synopsys) that can easily characterise foundation IPs to estimate power and performance of an SoC at any custom corner with substantial accuracy using reference ".lib" files.

Ensuring accuracy

In order to generate an accurate custom corner ".lib" file, one must ensure that a reference ".lib" file, which is already provided by an IP vendor, can be generated using the setup. The better co-relation achieved ensures more accurate ".lib" generation for the custom corner. Various options and settings available in the tool enable proper alignment of setup to adhere to the processes followed by different vendors to generate highly accurate ".lib" files. The tool also provides the flexibility to choose between different simulator environments available in the market (e.g., HSpice, Spectre).

Case study

A case study illustrating the success of custom corner characterisation performed on 28nm foundation IP is one where Open-Silicon used Synopsys' SiliconSmart characterisation tool to generate highly accurate results. To begin, an available standard corner .lib file was generated using a characterisation tool to ensure proper correlation. In this case, we re-characterized the scan flip-flop's typical corner .lib provided by the vendor (nominal voltage and 25C temperature). The results show that the correlation was very accurate. In the graphs below, one can see that the blue reference curves are almost entirely overlapped by the orange test curves.

Comparison of leakage power

Comparison of energy (dynamic power)

Comparison of delay

When such correlations are obtained, one can confidently rely on the setup to generate any customer corner .lib files as needed by the design.

Conclusion

The historical process of using extrapolation to measure a standard cell library's performance to changing voltage or temperature is starting to fade away. The complexity involved, the effort required, and the accuracy of constraints required means that a traditional extrapolation process is simply un-affordable. Characterisation tools, by comparison, can easily execute a handful of commands, generate highly accurate (close to 100%) results and deliver more efficiency. The end result is that today's characterisation tools offer a very good solution for extracting the best performance out of an ASIC/SoC for any specified PVT operating conditions.