Innovotek -News & BLOG

A blog about the news of the latest technology developments, breaking technology news, Innovotek Latest news and information tutorials on how to.

Modern ASIC Design Trends

- Font size: Larger Smaller

- Hits: 14018

- 0 Comments

- Subscribe to this entry

- Bookmark

Robert Troy, from ON Semiconductor details the way ASIC design is moving forwards and the different trends that are being seen.

Robert Troy, from ON Semiconductor details the way ASIC design is moving forwards and the different trends that are being seen.

Over the last decade many OEMs covering a broad cross section of different industry sectors have made clear their intention to gradually move away from the use of application specific integrated circuits (ASICs).

Instead they will rely more heavily on standard off-the-shelf components.

The reasoning behind this was primarily that it would allow them to push down overall costs and reduce their engineering resource.

However, in reality this has rarely happened, as within the last 3 to 4 years many of these companies have actually bolstered their design teams and continued to follow a predominantly ASIC centric approach to their system designs, so that they can maintain utmost differentiation from their rivals in increasingly competitive markets. Nevertheless it is evident that the ASIC landscape is going through a dramatic transformation and OEMs must respond to this accordingly.

ASIC considerations

There are various factors that need to be considered when undertaking ASIC implementation in order to ensure that the system design into which the chip is incorporated is as effective as possible, while the associated costs and the development time are both kept to a minimum. Over the course of the following article, these will be discussed.

Generally speaking, the key parameters involved in any ASIC implementation are performance, power, chip size, unit cost, functionality, non-recurring engineering (NRE) charges and time-to-market considerations.

There are a multitude of different trade-offs that can be made to designs in order to augment it for one (or more) of these parameters, but clearly if a customer wishes to witness a boost in a certain aspect of the ASIC’s characteristics it will come through making sacrifices elsewhere.

For example, in a portable consumer design it will be considered highly advantageous to keep the ASIC’s power consumption as low as possible, so that the end product’s battery life can be extended. It is also likely that there will be space constraints to take into account too. If these two demands are to be adequately met, then some compromises on the breadth of features that can be supported or the speed at which the ASIC can operate are likely to be needed.

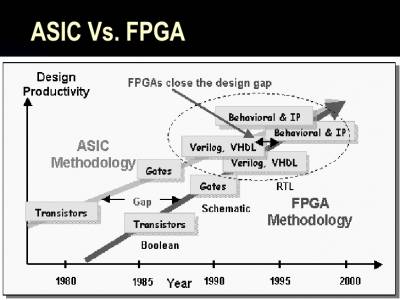

FPGAs vs ASICs

Though programmable logic has been pitched as a substitute for standard cell technology, in reality FPGAs can’t deliver what ASICs can.

They have flexibility in terms of making changes to the design either during the development process providing the capability for early prototyping of the hardware or a development tool for software to reduce risk, or at a later stage when the end product needs revamping, but when it comes to the sort of optimization that is possible for an ASIC they can’t compete.

If an engineer bases their design on any FPGA series then they will be subject to restrictions in terms of the dimensions of the different chips in that series, the number of look-up tables (LUTs) that are available, etc..

With an ASIC it is entirely different - the system designer effectively has a blank canvas. There is far more scope when it comes to parameters like board space utilization, power budget, operating speed – all that has to be decided upon is which of these are the highest priority. In many cases, of course, system designers will want all of them at once.

This is why consultation is paramount. In the past ASIC design and implementation was undertaken with very little dialogue between the system designer and those doing the work. The complexity of the design, the more acute time and cost constraints, plus the performance demands involved mean that this is no longer advisable.

There should be detailed discussion between the parties concerned at the earliest stages. This would include a discussion of process technology choice that will have a large impact on the scope of the ASIC development and the functionality that is possible to implement. This will mean that customers are aware of what is achievable and their expectations can be kept under control - as a result the project can be completed on schedule and costly re-spins can be avoided.

Standard interconnects

In many cases system designers are addressing the issues now affecting ASIC implementation by employing standards to define their systems interconnect, processor subsystems and external interfaces.

There are popular processors and subsystems that share a common interconnect bus - thereby enabling code portability from one device to the next. IP blocks that are compliant with high speed interconnect protocols with verifiable standards (such as PCI Express, Ethernet or MIPI) allow the system designer to utilize the standard physical interface and controller blocks and know that compatibility will not be an issue once the ASIC is produced.

Many high bandwidth memory interface standards are also available along with silicon-proven interfaces that can be leveraged within the design. The application of these standards facilitates the reuse of proven IP blocks in ASIC designs and thereby mitigates the risk of errors arising that will impinge on the project, either technically or financially speaking.

Often customers will overestimate what they need from the ASIC design. They will ask for inclusion of high performance processor cores (such an ARM Cortex A family and PowerPC 460) or high speed serial interface (such as USB 3.0), when in fact by being slightly less ambitious with regard to the spec, an ASIC that is more than adequate can be realized with the shortened development times or less acute NRE expense.

Today’s system architects and designers are left with some difficult choices to make. Conventional thinking says that they can either decide to do all of the implementation work and manage the manufacturing, assembly and test flows themselves or alternatively they can engage with small design houses and foundries to meet their system requirements.

ASIC design flow

Though the latter means that some of the activities involved can be offloaded, in reality there still a definite need for the system designer to oversee the design flow, as well as the packaging and testing, since any hitch here could mean that the investment is wasted.

An alternative to either engaging with a design house and foundry combination or attempting to carry out the work using its own engineering staff is for the OEM to partner with a semiconductor manufacturer/vendor which has an established ASIC business.

Though the number of semiconductor companies doing so has become more limited in recent times, there are still companies that offer comprehensive ASIC implementation services. Following this route allows the OEM to benefit from the manufacturer/vendor’s experience of working with different processes, so that the best fit for a particular set of application requirements can be selected, as well as knowing which particular IP blocks work well together so that overall system performance is heightened.

For example, for previous design projects it may have been ascertained that some MAC and PHY IP block permutations are very successful when adding interconnect functionality to an ASIC design using a certain process technology. Furthermore, though ASICs offer a higher degree of application security than alternative IC solutions there is increasing anxiety throughout the industry about counterfeiting. It is therefore critical that OEMs are aware of the commercial impact that this can potentially have. This adds to the impetus for them to liaise with a company that has the capacity to safeguard against such problems.

Summary

A variety of business-related and technology-related pressures have driven a major shift in the strategies taken by OEMs when embarking on new system designs that employ ASICs. ON Semiconductor is well positioned to address the changing face of the ASIC market. It provides its customer base with ASIC implementation services and semiconductor manufacturing expertise using a mix of advanced technologies from its own fabs and those of its associated foundry partners. The company also has the capacity to offer clients access to its team of highly proficient IP experts, so that system designers are able to make informed decisions when it comes to dealing with the trade-offs based on performance, power, cost, functionality, etc. that will mean their systems are fully optimized for the particular task they are being designed to execute.